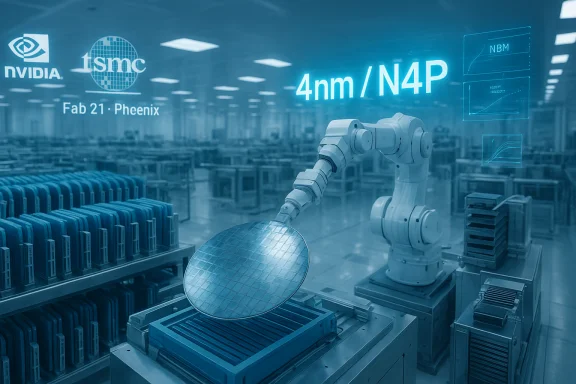

Nvidia and TSMC quietly marked a turning point in the U.S. semiconductor landscape this week when the first Blackwell wafer intended for Nvidia’s next-generation AI GPUs rolled out of TSMC’s Fab 21 near Phoenix — a milestone that signals both real industrial progress and an array of new technical, logistical, and geopolitical questions for the AI supply chain.

The Blackwell family is Nvidia’s flagship GPU architecture for the current wave of large-scale generative and reasoning AI, and Blackwell variants power everything from data‑center racks to new desktop “DGX” workstations. Nvidia publicly celebrated the moment: CEO Jensen Huang visited TSMC’s Phoenix facility and signed the first Blackwell wafer produced on U.S. soil, underscoring how Nvidia frames Blackwell as the engine for the next generation of AI systems.

TSMC’s Phoenix site (often referenced as Fab 21) is the company’s first advanced-node manufacturing site in the United States. The plant has been configured to run TSMC’s 4‑nanometer family (N4, N4P/4NP variants) in its first production phases and began ramping volume in 2025. That 4‑nm capability is what enabled customers such as Apple to manufacture A16 and related chips in small-scale, U.S.-based runs prior to the Blackwell wafer milestone.

This event is more than a PR moment: it represents the convergence of three trends that will define the next chapter of cloud AI infrastructure — hyperscaling demand for accelerator silicon, incremental national onshoring of advanced fabrication, and the ongoing structural complexity of packaging and test which still ties lead-edge chips to global supply chains.

Two things are important to parse:

Yet the celebration should be balanced with sober technical realism. Packaging, HBM integration, and system assembly remain complex, capital‑intensive, and geographically distributed operations. The Phoenix wafer represents major progress, not an instant decoupling from global supply chains. For organizations planning Blackwell‑era deployments, the right posture is pragmatic: capitalize on the improved wafer availability while diligently modeling the remaining bottlenecks — packaging timelines, power and cooling constraints, and the slow timelines needed to build full domestic packaging and memory ecosystems.

This milestone is a genuine structural step for the AI hardware industry: one wafer signed in Phoenix is both a symbol and an operating pivot — powerful and important, but still one stage in a long industrial journey.

Source: Techzine Global Nvidia and TSMC start production of Blackwell chips

Background

Background

The Blackwell family is Nvidia’s flagship GPU architecture for the current wave of large-scale generative and reasoning AI, and Blackwell variants power everything from data‑center racks to new desktop “DGX” workstations. Nvidia publicly celebrated the moment: CEO Jensen Huang visited TSMC’s Phoenix facility and signed the first Blackwell wafer produced on U.S. soil, underscoring how Nvidia frames Blackwell as the engine for the next generation of AI systems. TSMC’s Phoenix site (often referenced as Fab 21) is the company’s first advanced-node manufacturing site in the United States. The plant has been configured to run TSMC’s 4‑nanometer family (N4, N4P/4NP variants) in its first production phases and began ramping volume in 2025. That 4‑nm capability is what enabled customers such as Apple to manufacture A16 and related chips in small-scale, U.S.-based runs prior to the Blackwell wafer milestone.

This event is more than a PR moment: it represents the convergence of three trends that will define the next chapter of cloud AI infrastructure — hyperscaling demand for accelerator silicon, incremental national onshoring of advanced fabrication, and the ongoing structural complexity of packaging and test which still ties lead-edge chips to global supply chains.

What exactly happened in Phoenix?

The production step that matters

TSMC and Nvidia announced that Blackwell wafer production reached volume at Fab 21 near Phoenix. In practical terms, “wafer production” here means that patterned wafers — the multilayered semiconductor canvases containing many individual GPU dies — are being produced using advanced lithography and process flows on U.S. soil. The ceremony included Nvidia’s CEO signing the wafer to mark the milestone.Two things are important to parse:

- Volume wafer fabrication is not the same as final GPU assembly. The wafers produced in Phoenix will still flow through a global packaging and assembly chain that includes advanced silicon interposers, high-bandwidth memory (HBM) integration, and thermal/power packaging steps. Some of those packaging capabilities remain concentrated in Asia today; U.S. packaging capacity is expanding but not yet universal for the most advanced GPU products.

- The Phoenix plant is running TSMC’s 4‑nanometer‑class process (N4 family / 4N/4NP variants) in this production phase. That node is highly capable for many modern accelerators and system‑on‑chips; it is a couple of generations behind the absolute bleeding edge (2nm and related nodes), but it is fully modern and has been the workhorse for a long list of high-volume products.

Who’s involved where

Nvidia designs the Blackwell architecture and contracts manufacturing to TSMC. For packaging and assembly in Arizona, Nvidia has partnered with contract packagers and test houses — notably Amkor Technology and Siliconware Precision Industries (SPIL) — which are working alongside TSMC and Nvidia to convert wafers into finished GPUs and systems. Meanwhile, Nvidia is expanding its U.S. footprint further by building DGX supercomputer assembly lines in Texas with manufacturing partners. Mass production at the Texas facilities is expected to ramp in the next 12–15 months.The Blackwell architecture: why this wafer matters

What Blackwell brings to AI workloads

Blackwell is explicitly designed for large-model workloads and reasoning-focused AI. Compared with the previous Hopper generation, Blackwell introduced:- A rebuilt Transformer Engine optimized for the attention-heavy workloads of language and multimodal models.

- A Decompression Engine intended to accelerate database-style queries and compressed token pipelines.

- New low‑precision formats and tensor core enhancements (notably NVIDIA NVFP4 in Ultra variants) that increase throughput for inference and reduce memory pressure.

Blackwell Ultra: tangible numbers

Nvidia’s technical materials for Blackwell Ultra describe a dual‑die design, massive HBM capacities, and a new NVFP4 format that enables very high dense throughput. The Ultra variant is quoted in Nvidia materials and multiple independent technology outlets as delivering roughly 15 petaFLOPS of dense NVFP4 compute for the Ultra GPU in certain configurations (higher or different numbers appear when vendors describe rack‑scale aggregations). Those numbers are real in the context of Nvidia’s new precision formats and are meaningful for comparing architecture generations.Supply chain realities and why wafer production isn't the whole picture

Producing wafers is a vital step, but converting wafers into completed, shipping GPUs (and then into racks and systems) requires several additional complex operations:- Packaging and HBM integration. Many high-end Blackwell parts depend on advanced 2.5D/3D packaging, CoWoS/Co-EMIB styles, and tightly integrated HBM3E stacks. Those packaging operations require specialized tooling, test flows, and often different cleanroom footprints. At the moment, substantial capacity for the most advanced packaging remains in Asia, although Arizona is growing domestic packaging partners.

- Thermal and power validation. Blackwell-class GPUs push multi-kilowatt TGP envelopes in rack-scale configurations. Comprehensive thermal validation, liquid cooling integration, and power delivery validation happen after packaging and often in specialized assembly sites.

- System integration (DGX stacks). The GPUs must be integrated with Nvidia’s Grace CPUs, custom networking (NVLink, InfiniBand variants), and storage subsystems to build DGX SuperPODs and similar factory‑scale clusters. Nvidia’s stated intent is to assemble DGX systems in new U.S. factories, which shortens time-to-rack for some customers but does not magically remove earlier packaging dependencies.

Strategic implications: economics, politics, and industrial policy

Onshoring vs. strategic resilience

There are three intertwined gains from bringing Blackwell wafer production to Arizona:- Reduced lead times on wafers for U.S.-based customers and Nvidia’s domestic assembly lines.

- Political signaling around the CHIPS‑era goal of recreating a domestic advanced‑silicon ecosystem.

- Ecosystem development: attracting suppliers, packaging houses, memory partners, and talent to the same region shortens supply‑chain leg lengths.

Not a silver bullet

However, mass production of wafers in the U.S. does not eliminate dependencies:- Memory suppliers (HBM) and advanced packaging equipment remain concentrated in East Asia.

- IP, specialized process chemicals, and critical human expertise still cross borders.

- Complete onshoring will require sustained multi‑billion‑dollar investments in packaging, memory fabs, and workforce development — projects that take years, not weeks.

What this means for Nvidia, TSMC and customers

Nvidia’s playbook

For Nvidia, having wafers produced domestically helps with capacity planning and risk mitigation. Nvidia is simultaneously:- Ramping Blackwell system families (GB200/GB300, B200/B300), and new DGX product lines for both cloud and personal workstations.

- Building DGX assembly lines in Texas with Foxconn and Wistron to assemble supercomputer hardware domestically.

- Using its own AI, robotics, and digital‑twin tech to design and operate those new factories for efficiency.

TSMC’s calculus

TSMC benefits from large, long-term contracts with a customer of Nvidia’s scale while expanding its own U.S. footprint. The Phoenix fab’s initial 4‑nm output enables TSMC to prove yield parity at scale on foreign soil and sets the stage for later introduction of 3‑nm and 2‑nm processes in Arizona as demand warrants. TSMC’s CEO has signaled interest in accelerating U.S. 2‑nm timelines and adding land for more fabs, reflecting that AI demand is reshaping process roadmaps and capital deployment.Technical and operational risks

Packaging bottlenecks

While wafer production is now domestic, the most advanced packaging steps — interposers, HBM stack integration, wafer‑level chip‑to‑chip bonding — remain a potential bottleneck. Until advanced packaging capacity scales domestically, there will still be cross-border flows of wafers or substrates for assembly. Some industry accounts explicitly say fabricated wafers will be shipped back to Taiwan or other sites for final packaging in at least some product families. That reality reduces the immediate strategic independence that wafer onshoring implies.Thermal and power constraints in large deployments

Blackwell Ultra and GB300-class racks push the limits of datacenter power design and liquid cooling. As enterprises and hyperscalers install these systems, power provisioning, cooling water usage, and facility design will be non-trivial costs. These constraints may slow deployment pace in some markets and shift innovation toward more energy‑efficient inference formats and mixed CPU‑accelerator strategies. Nvidia’s own materials tout improvements in memory and quantization formats (NVFP4) to reduce memory footprints, but those gains trade off accuracy/engineering complexity in many production models.Geopolitical overhangs and policy fragility

This milestone does not remove the geopolitical dynamics that drive CHIPS-era investments. Export controls, tariff actions, and political rhetoric can still influence where certain equipment and personnel move. The U.S. push for onshoring is real, but it also depends on long-term policy consistency, training pipelines, and large capital flows — all subject to political cycles. Several outlets flagged how the moment is simultaneously a technological achievement and a political signal.What’s murky or misreported — cautious notes

- “A16 process” ambiguity: some reports and summaries mix product and process names. The term A16 usually refers to Apple’s A16 Bionic SoC (the chip), not a TSMC process node. TSMC’s internal roadmap uses various node labels (N2, N3, N4, A16 in some public summaries is used to denote an advanced process variant in 2026–2028 roadmaps). Several outlets reference an “A16 process” as shorthand for a future 1.6 nm-class node in TSMC marketing materials; that naming convention is not universal and can be misleading. Where sources use that phrase, treat it as shorthand for a planned advanced node family rather than a universally recognized process branding. This is a point to flag because press coverage and briefings sometimes conflate chip model numbers with fabrication node names. Caveat lector.

- Packaging and final assembly locus: it's accurate that wafers are being produced in Phoenix, but some credible reports indicate that final CoWoS or other highest-density packaging and HBM integration for specific top-bin Blackwell parts may still occur in Taiwan or other existing packaging hubs during an interim phase. That position is supported by independent technical reporting and supply‑chain analyses. Readers should not assume that wafer production in Arizona instantly replaced all offshore assembly and packaging routes.

- Performance numbers vary by metric: Nvidia’s performance claims for Blackwell and Blackwell Ultra often use new precision formats (NVFP4 / FP4, FP8, etc.) and present dense vs. sparse throughput. Different publications sometimes quote different figures depending on which format they emphasize (dense NVFP4 vs. sparse FP8). When comparing performance across announcements, check the precise precision and measurement conditions.

Strategic recommendations for IT leaders and procurement teams

- Treat onshored wafers as risk reduction, not elimination. The Phoenix production milestone reduces lead-time risk for wafers but does not remove packaging, memory, or thermal engineering dependencies. Plan multi-sourcing and staggered build runs accordingly.

- Revisit total cost of ownership (TCO) for Blackwell Ultra deployments. The new chips deliver huge raw throughput, but facility power, cooling, and networking costs rise alongside compute density. Model the full-stack operational expenses, not just silicon unit costs.

- Engage early with vendors on packaging timelines. If a vendor expects to deliver Blackwell rack units earlier because of U.S. wafer fabrication, confirm where advanced packaging will be performed and what that implies for delivery schedules.

- Monitor supplier expansion in Arizona and Texas. As Amkor, SPIL, Foxconn, and Wistron expand presence in the U.S., those investments will have practical implications for logistics and performance SLAs; procurement should capture firm commitments in contracts where latency or country-of-origin matters.

Broader market and competitive impacts

- Hyperscalers and cloud providers that signed early Blackwell orders may see shorter lead times and more predictable wafer supply; that could compress the time between design wins and full-rack delivery cycles for some cloud-native AI services.

- Regional industrial growth: Arizona’s high-tech manufacturing cluster is likely to grow around TSMC’s site, attracting packaging firms, test houses, and a talent pipeline. This has cascading economic effects for local supply chains, construction, and education programs.

- Global competition: The Phoenix wafer program helps the U.S. and its corporate partners present a counterweight to concentrated East Asian fabrication, but it will not instantly displace the decades‑long concentration of packaging and memory supply there. Expect continued interdependence for years to come.

Conclusion

The start of Blackwell wafer production at TSMC’s Arizona fab is a concrete technological and political milestone: it converts an abstract CHIPS‑era aspiration into physical wafers fabricated on U.S. soil, and it gives Nvidia direct, nearer-term access to a crucial part of the AI hardware pipeline. That step matters for capacity, resilience, and the optics of onshoring advanced manufacturing.Yet the celebration should be balanced with sober technical realism. Packaging, HBM integration, and system assembly remain complex, capital‑intensive, and geographically distributed operations. The Phoenix wafer represents major progress, not an instant decoupling from global supply chains. For organizations planning Blackwell‑era deployments, the right posture is pragmatic: capitalize on the improved wafer availability while diligently modeling the remaining bottlenecks — packaging timelines, power and cooling constraints, and the slow timelines needed to build full domestic packaging and memory ecosystems.

This milestone is a genuine structural step for the AI hardware industry: one wafer signed in Phoenix is both a symbol and an operating pivot — powerful and important, but still one stage in a long industrial journey.

Source: Techzine Global Nvidia and TSMC start production of Blackwell chips