Microsoft’s Azure Cobalt 200 arrives as a radical second act in its custom‑silicon playbook: a chipletized Arm-based server SoC that packs 132 Arm Neoverse V3 cores, a 12‑channel DDR5 memory interface, built on TSMC’s 3 nm process, and a set of on‑SoC accelerators and per‑core power controls aimed squarely at cloud‑native scale‑out workloads.

Background / Overview

Microsoft’s Cobalt program began as a strategic bet to own more of the hardware stack and tune compute for Azure’s scale, following the same hyperscaler playbook used by other cloud vendors that build custom Arm silicon. The Cobalt 200 continues that trajectory by adopting Arm’s newest server subsystem (CSS V3), pushing transistor density with TSMC 3 nm, and combining a high core count with a wide memory fabric and integrated accelerators to reduce host software overhead. Microsoft positions Cobalt 200 as a performance‑and‑efficiency uplift over the previous generation, claiming up to 50% higher performance vs Cobalt 100 and describing the first production servers as already running in Microsoft datacenters, with broader customer availability scheduled for 2026. Those are company claims that require independent validation when public instance types appear.Architecture deep dive

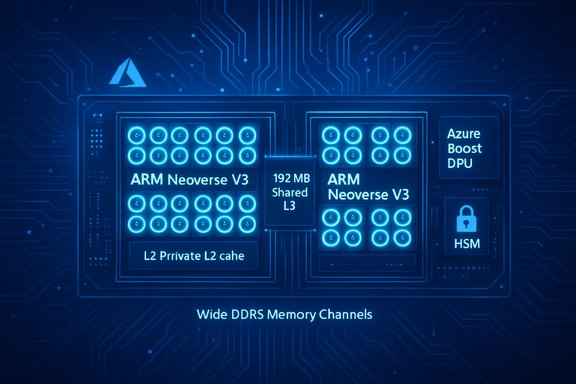

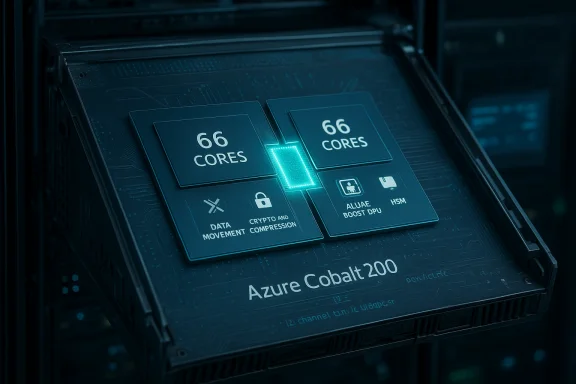

Chiplet topology and core count

At the package level Cobalt 200 is a two‑chiplet SoC with a high‑bandwidth die‑to‑die link tying the two compute tiles into a single socket. Microsoft reports 132 active cores per SoC; industry coverage and Microsoft imagery show this implemented as 66 cores per chiplet (66 + 66). That layout lets Microsoft scale core count while managing yield and thermal density with chiplets rather than a single monolithic die. Important note on an apparent specification edge case: Arm’s Neoverse CSS V3 is formally specified as supporting up to 64 cores per die in its published per‑die spec, while Microsoft’s design shows 66 active cores per tile. That difference may reflect licensee flexibility in CSS V3 implementations, the use of spare/yield cores, or a vendor‑level customization of the subsystem; it’s a detail worth flagging for verification because it speaks to how closely vendors map Arm’s reference subsystem to their production parts.Core microarchitecture and cache hierarchy

Cobalt 200 is built on the Arm Neoverse V3 family via Arm’s CSS V3 blueprint, giving Microsoft a modern, high‑IPC core design and a fabric tuned for confidential compute and high throughput. Microsoft lists 3 MB of L2 cache per core (a very large private L2 allocation) and 192 MB of shared L3 system cache for the entire SoC. That L2/L3 balance signals an architecture optimized for on‑core locality and scaling of many lightweight threads rather than purely boosting single‑thread peak frequency. Arm’s public material says CSS V3 delivers a flexible memory and cache topology and is expressly designed to let partners tune cache sizes for workload targets; Cobalt 200’s unusually large private L2 per core is therefore feasible in a CSS‑based design but is a deliberate tradeoff that favors the kinds of containerized, thread‑dense services Azure runs.Memory and I/O fabric

Each chiplet exposes six memory channels, yielding 12 memory channels per socket when both chiplets are considered together. The result is a very wide DDR5 memory subsystem intended to feed the 132 cores and reduce memory bandwidth contention under heavy multi‑threaded loads. The package also carries high‑speed I/O (PCIe Gen5/CXL lanes are possible via CSS V3) and die‑to‑die links compatible with UCIe or custom PHYs.On‑SoC accelerators and stack integration

Microsoft integrates several specialized engine blocks on the SoC:- Data Movement Accelerator — to speed DMA‑style transfers and reduce CPU overhead on streaming I/O.

- Crypto and Compression Accelerators — to offload common cloud tasks (TLS, disk encryption, network compression).

- Other Azure‑specific IP — tight integration points for the Azure Boost DPU and an Azure‑integrated HSM are called out in Microsoft’s materials to reduce host CPU cycles and shorten secure key paths.

Per‑core DVFS and power management

A headline feature for Cobalt 200 is per‑core Dynamic Voltage and Frequency Scaling (DVFS) — the ability to set different performance points on each core independently. In theory this enables fine‑grained energy proportionality: idle or background threads can sit at low power while latency‑sensitive cores run faster, saving energy across the rack.In practice per‑core DVFS increases complexity:

- Power delivery networks must support many operating points across a socket.

- Thermal behavior and neighbor‑core interference must be modeled carefully.

- OS scheduler, hypervisor, and firmware must expose and use the per‑core controls effectively.

What Microsoft claims — and what needs verification

Microsoft’s public statement and the Ignite Book of News list a set of bold promises:- 132 active Arm Neoverse V3 cores per SoC with a chiplet 66+66 layout.

- 3 MB L2 per core and 192 MB L3 system cache.

- Fabrication on TSMC 3 nm for improved energy per operation.

- Integration with Azure Boost (DPU) and an on‑package HSM for tightened security and offload.

- A marketing figure of “up to 50%” performance improvement over Cobalt 100.

- The “up to 50%” improvement is a vendor figure. Microsoft’s slide set and blog indicate the gains are measured against targeted cloud‑native workloads and reflect simulation and internal measurements; they should be treated as guidance rather than as a universal uplift across all workloads until independent benchmarks appear.

- Yield and production behavior on TSMC 3 nm: Microsoft says first production servers are live, but large‑scale availability depends on foundry capacity, yield, and supply chain scheduling. Public availability is slated for 2026; exact timeline and pricing will determine commercial impact.

- The 66 cores per tile vs Arm CSS V3’s published up to 64 cores per die raises a specification question that Microsoft and Arm have not publicly walked through in fine detail; this needs clarifying to fully reconcile the design with Arm’s per‑die spec.

Packaging, thermal design and server integration

Microsoft showed a test system photo that pairs two Cobalt 200 chips with its NICs and E1.S NVMe devices in a dual‑chiplet, dual‑socket arrangement. The cooling approach looks familiar to Microsoft’s prior server designs: larger heatsink with a thick perimeter around the socket, tuned for the company’s airflow and high‑ambient temperature deployment targets. Observers noted an unusually thick fin perimeter and eight retention screws around the socket area, suggesting custom mechanical engineering to manage the higher power density at the socket plane.From an operations standpoint, the chiplet approach reduces monolithic die risk but introduces packaging complexity (die‑to‑die link integrity, interposer or UCIe implementation, NUMA visibility across chiplets). Microsoft’s internal telemetry and firmware will decide how transparent those topologies are to guest OSes and hypervisors.

Competitive context: where Cobalt 200 fits

- Against AWS Graviton: AWS’s Graviton family is a mature, deployed Arm ecosystem with many public instance types and broad software support. Microsoft’s Cobalt effort targets the same market of cost‑sensitive scale‑out workloads but differentiates with tighter Azure stack integration (DPUs, HSM) and a particular focus on per‑core power control and chiplet scaling. Customers will choose by total cost, available instance shapes, and software compatibility.

- Against NVIDIA Grace (and Grace‑based systems): NVIDIA’s Grace CPU efforts targeted HPC and AI memory‑bound workloads and use Arm‑based cores tuned for large memory bandwidth. Cobalt 200 emphasizes consolidation, energy proportionality, and integrated offloads for cloud services rather than serving primarily as an AI training CPU. Feature sets overlap in being Arm‑based, but target profiles differ.

- Against Intel Xeon 4th Gen: Intel has been embedding accelerators (AMX, QAT, DSA) directly in Xeons to accelerate AI, crypto, and data movement. Microsoft’s inclusion of crypto/compression and dedicated data movement hardware in Cobalt 200 mirrors that trend. The difference is Microsoft’s co‑design with Arm CSS V3 and cloud‑native integration, while Intel’s approach is x86‑centric with a long software stack pedigree. Real competitiveness will hinge on price‑performance, availability and software maturity.

Practical implications for Azure customers and IT teams

Cobalt 200 will matter most for workloads where consolidation, throughput per rack, and energy per operation drive economics:- Web front ends, microservices, proxies, distributed caches, smaller‑model CPU inference, and many containerized services will likely benefit from increased core density and on‑chip accelerators.

- Memory‑heavy or I/O‑bound workloads will need to be validated; the wide memory interface is encouraging but real‑world NUMA behavior, interrupt routing and DPU offload interactions are the practical tests.

- Measure end‑to‑end time‑to‑solution and cost‑per‑job on a representative workload rather than relying on single microbenchmarks.

- Include power and telemetry in pilot runs — energy per operation is a core part of Microsoft’s pitch.

- Validate binary compatibility and behavior for any x86‑only enterprise software; identify replacement or recompilation needs for Arm64.

- Test network, storage and cryptographic workloads with and without Azure Boost/DPU offload to quantify host CPU savings.

- Publish and compare methodologies so that results can be reproduced across teams and vendors.

Risks, supply constraints and operational unknowns

- Foundry capacity and yield: Fabrication on TSMC 3 nm is a strategic advantage but also a capacity risk. Hyperscalers compete aggressively for advanced node allotments; early deployment and internal use are plausible, but broad availability can be staggered.

- Software and ecosystem friction: Although Arm‑on‑server support has matured rapidly, enterprise ecosystems still contain x86 artefacts. Migration costs and testing for legacy middleware and third‑party drivers remain real.

- Vendor marketing vs. reproducible outcomes: Microsoft’s “up to 50%” claim is presented as a generational uplift for cloud‑native workloads; independent, reproducible third‑party benchmarks will be necessary to translate that into procurement decisions. Customers should insist on representative tests performed under real‑world conditions.

- Operational complexity of per‑core DVFS: Fine‑grained DVFS requires sophisticated scheduler and telemetry integration. Poorly coordinated power/performance policies could harm tail latency or create noisy neighbor effects in multi‑tenancy environments.

Verification, benchmarking and what to watch next

Given Microsoft’s claims and the architectural shifts in Cobalt 200, the following are the highest‑value items the community and IT teams should watch for in the coming months:- Publication of public Cobalt 200 VM SKUs, pricing, and regional availability timelines (Microsoft’s announcement points to 2026 availability).

- Independent benchmarks across a matrix of workloads: scale‑out web services, container density, Redis/Postgres, CPU inference (small LLMs), and I/O/crypto throughput — with power‑aware metrics (watts per request).

- Deep technical write‑ups showing how the 66+66 chiplet split maps to Arm’s CSS V3 specifications, and whether the extra cores are spares/yield‑related or an explicit CSS configuration that exceeds the public per‑die baseline.

- Documentation or whitepapers detailing how Azure exposes per‑core DVFS to guests or whether it remains a Microsoft‑managed platform feature; details here will determine how much customers can tune energy/performance at the VM level.

Final analysis — strengths, strategic rationale, and potential downsides

Strengths and strategic wins- System‑level optimization: Microsoft is designing silicon to work with Azure’s DPU, HSM and service fabric — a powerful co‑design that can materially lower cost‑per‑workload at hyperscale.

- Modern building blocks: Using Arm CSS V3 gives Microsoft a faster path to production silicon with proven die‑to‑die interconnect and a tested ecosystem.

- Aggressive efficiency targets: Per‑core DVFS plus TSMC 3 nm process promises improved energy proportionality if software stacks leverage those controls effectively.

- Heterogeneous on‑SoC offloads: Integrated crypto, compression and data movement engines will reduce host CPU cycles for common cloud services — a pragmatic, revenue‑neutral efficiency play.

- Vendor‑claimed performance needs independent validation. The “up to 50%” metric will vary by workload; customers should require representative benchmarks.

- Supply and cost sensitivity around 3 nm. Advanced node runs are expensive and capacity constrained; that will affect instance availability and pricing early in the lifecycle.

- Operational complexity of per‑core DVFS and chiplet NUMA. Those features are powerful but raise scheduler, telemetry and firmware engineering demands; immature integrations can negate intended gains.

- Ecosystem migration costs. Organizations with x86‑only stacks may face nontrivial porting and validation burdens.

Conclusion

Azure Cobalt 200 is a consequential product for cloud infrastructure: it demonstrates Microsoft’s continued commitment to vertically integrating hardware and software to optimize TCO and efficiency for Azure services. Built on Arm’s Neoverse CSS V3 foundation and leveraging TSMC’s 3 nm process, the SoC bundles high core counts, large per‑core caches, a very wide memory interface, per‑core DVFS, and a set of on‑chip accelerators that reflect modern cloud economics.The architecture is plausible and strategically coherent — and multiple independent outlets and Arm’s own materials corroborate the key components of the design. That said, headline performance claims, real‑world efficiency, and platform ergonomics remain vendor‑provided assertions until independent, reproducible benchmarks and deployment data become available once public instance types arrive in 2026. Organizations planning pilots should prioritize representative, power‑aware testing, validate software compatibility, and model the operational implications of per‑core power control and chiplet topology before committing at scale.

Source: ServeTheHome Microsoft Azure Cobalt 200 Launched with 132 Arm Neoverse V3 Cores