Microsoft’s Maia 200 is not a subtle step — it’s a direct, public escalation in the hyperscaler silicon arms race: an inference‑first AI accelerator Microsoft says is built on TSMC’s 3 nm process, packed with massive on‑package HBM3e memory, and deployed in Azure with the explicit aim of lowering per‑token cost for production AI services. ia is Microsoft’s second‑generation in‑house accelerator program, following the experimental Maia 100. The company positions Maia 200 as a purpose‑built inference SoC that trades training versatility for inference density, predictable latency, and improved performance‑per‑dollar in production serving. Microsoft announced Maia 200 on January 26, 2026 and said it is already running in Azure’s US Central region with US West 3 slated next. These are vendor statements that multiple outlets quickly reproduced; independent, workload‑level verification remains pending.

Why an inference‑first chip? Training GPUs are optimized for mixed‑precision dense compute and wide flexibility, but the recurring cost of AI comes from inference: every user query and API call. By optimizing silicon, memory hierarchy, and datacenter fabric specifically for low‑precision, memory‑heavy inference patterns, hyperscalers can meaningfully lower the dollars‑per‑token for services like Microsoft 365 Copilot and hosted OpenAI models. Maia 200 is marketed as Microsoft’s engineering answer to that economic pressure.

Microsoft’s public materials and press coverage present a concise set of headline figures. Taken together they form the company’s value proposition for the chip:

That said, the most important caveats are operational and empirical: vendor‑reported peak metrics and perf/$ statements must be validated with independent, workload‑level benchmarks. The risk profile centers on quantization fidelity, the real‑world behavior of the Ethernet scale‑up fabric at cluster scale, and the operational realities of ramping a 3 nm product in volume.

For WindowsForum readers: treat Maia 200 as an early, high‑potential platform for inference hosting. Start the technical work now — quantify model readiness for FP8/FP4, build reliable benchmarks, and prepare operational playbooks — because if Microsoft’s perf/$ claims hold across your workloads, Maia 200 will change how Azure pricing and AI hosting choices are evaluated.

Maia 200 is not the end of Nvidia’s era, but it is a meaningful, practical counterweight. The next months of independent benchmarks, Azure region rollouts, and developer adoption will decide whether Maia 200 becomes a defining infrastructure play or a strategically valuable step in a longer first‑party silicon journey.

Source: Tbreak Media Microsoft Maia 200: AI chip to cut Azure costs | tbreak

Source: Technetbook Microsoft Azure Maia 200 AI Accelerator Unveiled Using TSMC 3nm Process for Inference

Why an inference‑first chip? Training GPUs are optimized for mixed‑precision dense compute and wide flexibility, but the recurring cost of AI comes from inference: every user query and API call. By optimizing silicon, memory hierarchy, and datacenter fabric specifically for low‑precision, memory‑heavy inference patterns, hyperscalers can meaningfully lower the dollars‑per‑token for services like Microsoft 365 Copilot and hosted OpenAI models. Maia 200 is marketed as Microsoft’s engineering answer to that economic pressure.

What Microsoft says Maia 200 is (headline claims)

What Microsoft says Maia 200 is (headline claims)

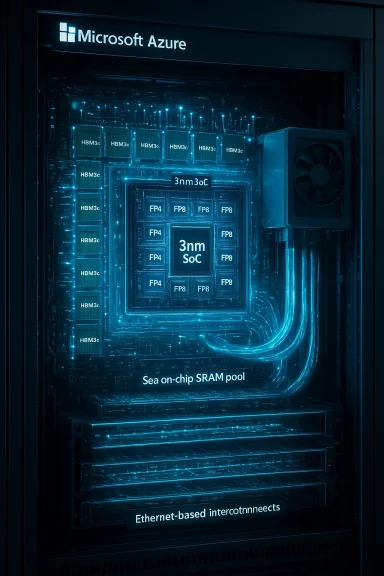

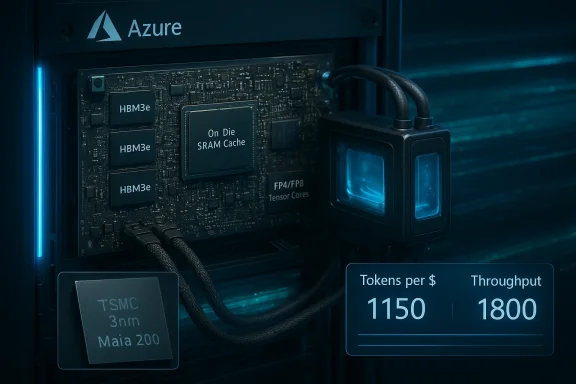

Microsoft’s public materials and press coverage present a concise set of headline figures. Taken together they form the company’s value proposition for the chip:- Process and transistor budget: Built on TSMC’s 3‑nanometer class process; Microsoft cites a transistor budget “over 140 billion” in multiple communications.

- Precision and compute: Native tensor hardware optimized for narrow‑precision inference (FP4 and FP8) and vendor‑stated peak throughput of >10 petaFLOPS (FP4) and >5 petaFLOPS (FP8) per accelerator.

- Memory subsystem: 216 GB of HBM3e on‑package with roughly 7 TB/s aggregate bandwidth, plus about 272 MB of on‑die SRAM for fast staging and caching.

- Thermals and power: A SoC thermal envelope in the neighborhood of ~750 W (Microsoft describes rack cooling and liquid/closed‑loop arrangements).

- Interconnect and fabric: A two‑tier, Ethernet‑based scale‑up fabric with a Microsoft‑designed Maia transport layer exposing ~2.8 TB/s bidirectional dedicated scale‑up bandwidth per accelerator and the ability to form collectives across thousands of accelerators (Microsoft cites clusters up to 6,144 accelerators).

- Software and tooling: A preview Maia SDK with PyTorch integration, a Triton compiler, optimized kernel libraries, and a low‑level programming language (NPL) plus simulators and cost‑calculator tools to ease model porting.

- Business claim: Microsoft states the Maia 200 is “the most efficient inference system Microsoft has ever deployed,” offering about 30% better performance‑per‑dollar for inference than the latest generation of hardware in its fleet.

Overview of architecture: where Maia 200 aims to win

Memory‑first design

At the heart of Microsoft’s argument is memory locality — that inference for large language models is bound more by moving bytes than by raw FLOPS. Maia 200’s package emphasizes a large, high‑bandwidth memory pool plus substantial SRAM to stage hot weights and KV caches, reducing trips to slower storage or cross‑device fetches.- Why it matters: In autoregressive generation, the model repeatedly accesses weights and large KV caches; keeping as much of that state near the compute fabric reduces tail latency and device fan‑out per token. Maia’s 216 GB HBM3e + 272 MB SRAM is explicitly engineered for that pattern.

Low‑precision native compute (FP4 / FP8)

Maia 200 targets aggressive quantization in hardware: native FP4 and FP8 tensor units dramatically increase math density compared with wider formats. That yields greater tokens‑per‑watt and tokens‑per‑dollar for models that tolerate lower precision.- Tradeoffs: Aggressive quantization increases software complexity. Not all models maintain identical quality under 4‑bit quantization; robust quantization flows, fallback paths, and per‑model validation are required to preserve accuracy and safety. Microsoft’s SDK and simulation pipeline are designed to help with that transition.

Ethernet‑based scale‑up fabric

Instead of relying on proprietary fabrics like InfiniBand/NVLink, Microsoft built a two‑tier scale‑up network over commodity Ethernet with a custom Maia transport and integrated NICs.- Claimed benefits: Economics (Ethernet at massive scale is very cost‑effective), standardization, and the ability to program consistent collectives across trays and racks.

- Key risk: Collective operations at hyperscaler scale are sensitive to congestion, tail behavior, and failure modes; delivering InfiniBand‑like determinism on Ethernet will require careful engineering and operational validation.

Cross‑checking the reporting: verification and caveats

I verified Microsoft’s primary claims against the company’s official blog post and multiple independent trade outlets.- Microsoft blog (official technical announcement) documents the core specs: TSMC 3 nm, 216 GB HBM3e, 272 MB SRAM, >10 PFLOPS FP4, >5 PFLOPS FP8, 750 W SoC envelope, Ethernet scale‑up design, and the SDK preview. These core claims are repeated in the official blog.

- Independent coverage from outlets such as The Verge and DataCenterDynamics (DCD) reprints the headline figures and focuses assessment on what matters in practice: memory bandwidth, interconnect, and quantization strategy. These outlets largely corroborate the vendor narrative while noting the need for workload measurements.

- Industry commentary emphasizes the economics: if Maia 200 truly delivers ~30% perf/$ improvements on production inference workloads, that advantage compounds rapidly at hyperscale and reshapes cost dynamics. Analysts also caution that transistor counts and peak PFLOPS are vendor‑reported marketing metrics and that real performance depends on end‑to‑end system behavior.

- Transistor count and peak FLOPS: These are vendor‑provided specs; independent measurement of transistor count or effective token throughput requires teardown or benchmark studies that are not yet public. Treat the numbers as credible design intentions but vendor statements, not neutral measurements.

- 30% performance‑per‑dollar: Microsoft’s perf/$ claims are central to the business case, but they are sensitive to workload mix, scheduling, and Azure pricing models. Independent workload evaluations are needed to confirm this advantage across a representative set of production models.

- Deployment scale: Microsoft says Maia 200 is deployed in US Central and will expand. Roll‑out cadence, global availability, and region‑by‑region capacity are operational decisions that will determine how meaningful the advantage is for external customers.

Strengths: where Maia 200 could truly move the market

- Purposeful systems engineering: Microsoft built Maia 200 as a joint play of silicon, memory, rack mechanics, network, and runtime. That systems perspective matters; performance at hyperscale is a platform problem, not just a die problem.

- Memory and bandwidth focus: By prioritizing on‑package HBM3e and on‑die SRAM, Maia 200 addresses the principal bottleneck for inference: data movement. For large models, that can reduce device fan‑out and latency spikes.

- Cost economics: A persistent, demonstrable ~20–30% improvement in inference perf/$ at cloud scale would translate into meaningful margin expansion for MS products and potentially lower prices for customers — a lever that hyperscalers can and do apply strategically.

- Software stack and openness: Early SDK access, PyTorch integration and Triton support signal Microsoft’s intent to reduce friction for model porting — a necessary move if customers are to adopt Maia‑native hosting.

- Operational control and supply diversification: Owning a first‑party accelerator reduces Microsoft’s dependence on any single vendor for inference capacity and gives it ng and price volatility in GPU markets.

Risks and open questions

- Quality vs. quantization: Aggressive FP4 adoption requires mature quantization tooling and extensive per‑model validation. Some models will adapt easily; others (safety‑critical or high‑precision generative systems) may degrade without careful work. This is a non‑trivial migration for many enterprise models.

- Fabric and scale challenges: Delivering deterministic collectives across thousands of accelerators using Ethernet and a custom transport is ambitious. Production behavior under partial failures, noisy neighbors, and mixed workloads will be the acid test.

- Supply chain and ramp: Manufacturing on TSMC’s 3 nm node enables density but comes with yield and capacity constraints that can affect ramp speed and geographic expansion. Microsoft will need to manage fab allocations and yield curves if it hopes to scale beyond pilot regions quickly.

- Ecosystem inertia: Nvidia’s GPUs, CUDA ecosystem, and marketplace momentum are significant. Even with better perf/$ on narrow cases, persuading broad swathes of customers to port models and workflows — or to switch hosting choices — takes time. Microsoft will have to match or exceed developer ergonomics to make headway.

- Vendor‑reported metrics: Peak PFLOPS and transistor counts are useful design signals but not proof of system performance. Independent benchmarks and head‑to‑head workload comparisons will be required to validate Microsoft’s claims across representative inference workloads.

What this means for IT leaders, developers, and WindowsForum readers

If you manage AI infrastructure or rely on Azure for model hosting, Maia 200 introduces both opportunity and a short action checklist.- For cloud architects: Start planning how you would evaluate Maia‑backed instances once they’re available in your preferred regions. Prioritize realistic inference workloads and measure end‑to‑end latency, tail percentiles, and cost per token — not just peak FLOPS.

- For ML engineers and devs: Begin assessing model quantizability. Run controlled experiments porting models to FP8/FP4 simulation backends, and validate output fidelity, calibration, and safety metrics. Use the Maia SDK simulator (preview) where available to measure performance and catch correctness issues early.

- For procurement and finance teams: Watch Azure region rollouts and pricing closely. A 20–30% reduction in inference TCO can change hosting decisions — but only if the performance and availability match your needs. Consider staged migrations for high‑volume endpoints.

- For operations and SREs: Prepare for different failure and observability modes. Maia’s Ethernet scale‑up fabric and dense trays will require new runbooks for network congestion, device restart policies, and thermal/cooling maintenance. Invest in telemetry that tracks per‑token cost and quality metrics.

- Request access to the Maia SDK preview if your models are latency‑sensitive or run at scale.

- Run a quantization fidelity study (FP8 and FP4) on a representative sample of models.

- Build a workload comparison framework that measures tokens/second, tail latency (95th/99th percentile), and tokens‑per‑dollar.

- Simulate network collectives and isolate failure patterns to evaluate how model sharding behaves in production.

- Keep a close eye on Azure regional availability and on Microsoft’s public benchmark papers or third‑party tests.

Competitive and market implications

Maia 200 is another clear signal that major cloud providers are moving to verticalize key parts of the inference stack. Amazon, Google, and others have been pursuing similar first‑party silicon strategies; Microsoft’s contribution is notable because it publicly commits a full systems approach — chip, package, network, racks, cooling and SDK.- For Nvidia: Maia 200 does not obviate Nvidia’s role in training or many inference scenarios, but it raises competitive pressure on inference economics and regional capacity allocation. Wall Street and markets have already signaled that Nvidia will remain central to the sector’s growth, but hyperscalers controlling part of the inference stack changes negotiation dynamics.

- For enterprise customers: More choices at the infrastructure layer can mean better pricing, but it also increases complexity in procurement and portability decisions. Enterprises must balance performance gains against engineering and validation cost of migration.

- For the broader ecosystem: If Maia’s Ethernet scale‑up fabric works at scale, it could shift how datacenter interconnects are engineered for AI workloads — making commodity networking more central to high‑performance clusters and reducing reliance on specialized, proprietary fabrics.

Verdict and final assessment

Maia 200 is a consequential, well‑engineered gamble by Microsoft: a systems‑level solution that targets the economics of inference where hyperscalers feel the most pain. The chip’s memory heavy architecture, narrow‑precision compute, and novel Ethernet scale‑up fabric are logical choices for inference density — and Microsoft’s integration of SDKs and runtime tooling reduces friction for adoption.That said, the most important caveats are operational and empirical: vendor‑reported peak metrics and perf/$ statements must be validated with independent, workload‑level benchmarks. The risk profile centers on quantization fidelity, the real‑world behavior of the Ethernet scale‑up fabric at cluster scale, and the operational realities of ramping a 3 nm product in volume.

For WindowsForum readers: treat Maia 200 as an early, high‑potential platform for inference hosting. Start the technical work now — quantify model readiness for FP8/FP4, build reliable benchmarks, and prepare operational playbooks — because if Microsoft’s perf/$ claims hold across your workloads, Maia 200 will change how Azure pricing and AI hosting choices are evaluated.

Maia 200 is not the end of Nvidia’s era, but it is a meaningful, practical counterweight. The next months of independent benchmarks, Azure region rollouts, and developer adoption will decide whether Maia 200 becomes a defining infrastructure play or a strategically valuable step in a longer first‑party silicon journey.

Source: Tbreak Media Microsoft Maia 200: AI chip to cut Azure costs | tbreak

Source: Technetbook Microsoft Azure Maia 200 AI Accelerator Unveiled Using TSMC 3nm Process for Inference