Microsoft’s Maia 200 is the latest, bold step in a multi-year pivot by hyperscalers to own the silicon that runs generative AI — a purpose-built, inference-first accelerator that promises significantly lower token costs, higher utilization for large models, and a path away from sole reliance on GPU vendors.

Cloud providers have been quietly designing custom AI silicon for years to reduce costs, control supply chains, and tune hardware to their own model workloads. Google’s Tensor Processing Units (TPUs), Amazon’s Inferentia and Trainium families, and Meta’s MTIA all signal the same strategic thesis: when AI workloads are predictable, vertical integration of hardware and software can unlock better performance-per-dollar and greater operational control. Microsoft’s Maia 200 follows that pattern as a second-generation, inference-focused chip after the company’s initial Maia 100 effort.

Maia 200 is positioned explicitly as an accelerator for inference — the stage of AI operation where trained models respond to user queries, do retrieval-augmented generation, or produce tokens for chat and assistant scenarios. That narrow focus lets Microsoft optimize for low-precision math (FP4/FP8), memory movement, and dense serving scenarios rather than the high-precision, bandwidth-heavy demands of model training. Microsoft frames this as a way to improve responsiveness and reduce token economics for services like Microsoft 365 Copilot and Microsoft Foundry.

That said, the usual caveats apply: vendor claims need independent validation; FP4/FP8 migration requires careful per-model testing; and CUDA’s software ecosystem remains a formidable moat. For enterprises, the prudent path is one of measured experimentation: pilot Maia-accelerated serving for workloads that are already robust to quantization and that would benefit most from reduced token costs, while retaining GPU options for workloads that demand the NVIDIA ecosystem or higher precision.

Maia 200 isn’t just another silicon announcement — it’s the next chapter in cloud providers’ long march to owning not only the data center but the math that runs on it. Whether that translates into better price-performance for customers will depend on Microsoft’s rollout, the availability of Maia-optimized instances, and the outcomes of independent validation. For now, Maia 200 raises the stakes in the custom-silicon race and makes the case that in the era of generative AI, the company that co-designs models, software, and chips can command meaningful advantages.

Source: YourStory.com Microsoft Maia 200 and the ongoing evolution of custom AI silicon

Background

Background

Cloud providers have been quietly designing custom AI silicon for years to reduce costs, control supply chains, and tune hardware to their own model workloads. Google’s Tensor Processing Units (TPUs), Amazon’s Inferentia and Trainium families, and Meta’s MTIA all signal the same strategic thesis: when AI workloads are predictable, vertical integration of hardware and software can unlock better performance-per-dollar and greater operational control. Microsoft’s Maia 200 follows that pattern as a second-generation, inference-focused chip after the company’s initial Maia 100 effort. Maia 200 is positioned explicitly as an accelerator for inference — the stage of AI operation where trained models respond to user queries, do retrieval-augmented generation, or produce tokens for chat and assistant scenarios. That narrow focus lets Microsoft optimize for low-precision math (FP4/FP8), memory movement, and dense serving scenarios rather than the high-precision, bandwidth-heavy demands of model training. Microsoft frames this as a way to improve responsiveness and reduce token economics for services like Microsoft 365 Copilot and Microsoft Foundry.

What Maia 200 is claiming to deliver

Silicon process, transistor count, and peak compute

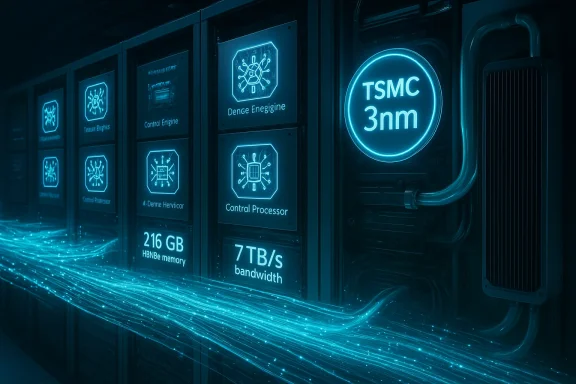

- TSMC 3nm process — Maia 200 is fabricated on a 3-nanometre process node from TSMC, placing it at the leading edge of foundry technology for commercial cloud silicon.

- Transistors — Microsoft states Maia 200 contains more than 140 billion transistors. Independent reporting cites “over 100 billion” in early coverage, but Microsoft’s own technical blog specifically uses the 140B+ figure. Where transistor counts are published by vendors, they reflect packaging and die-size choices and are best read as vendor-declared metrics.

- FP4 / FP8 peak FLOPS — Microsoft rates Maia 200 at over 10 petaFLOPS of performance in 4‑bit floating-point precision (FP4) and over 5 petaFLOPS at 8‑bit (FP8) precision. These figures are the chip’s peak mathematical throughput in low-precision modes and are comparable to the new low-precision metrics vendors emphasize for inference.

Memory and feeding the compute

One of Maia 200’s headline differentiators is its memory subsystem:- 216 GB of HBM3e (High Bandwidth Memory) delivering ~7 TB/s (terabytes per second) of memory bandwidth, according to Microsoft’s spec sheet.

- 272 MB of on-die SRAM used as an ultra-fast scratchpad for token-level data reuse, reducing trips to external DRAM/HBM and improving energy efficiency and latency.

Chip architecture and system scale

Microsoft describes Maia 200 as built from repeated autonomous units called tiles. Each tile contains:- a math-specialized engine (for dense tensor operations), and

- a more general-purpose processor for control and non-matrix tasks.

Thermal and power envelope

- Maia 200 targets a 750-watt thermal/power envelope per accelerator and uses a second-generation closed-loop liquid cooling system integrated into the server rack design. Microsoft points to a “sidekick” radiator and closed-loop approach to contain power density while maximizing rack utilization.

Software and developer experience

A chip without software is a paperweight. Microsoft is shipping the Maia SDK with:- PyTorch integration and ONNX Runtime support for standard model portability,

- a Triton compiler (the open-source project created originally at OpenAI) for high-performance kernel generation, and

- a low-level programming language called NPL for expert kernel authors pushing the silicon to its limits.

How Maia 200 fits the competitive landscape

No vendor operates in a vacuum. Maia 200 will join a heterogeneous field:- NVIDIA remains the dominant commercial supplier with the Blackwell Ultra family (reported at 208 billion transistors and up to 15 petaFLOPS in NVFP4 for the Ultra variant). NVIDIA’s strength is a vast software ecosystem anchored by CUDA, mature tooling, and extensive third-party optimization.

- AWS continues to scale its Trainium (for training) and Inferentia (for inference) lines. Amazon’s Trainium3, for example, advertises 3nm process advantages and per-chip FP8 ratings that target both training and inference scenarios in its EC2 UltraServers. Measuring apples-to-apples between FP4, FP8, and vendor-specific data types requires careful attention because precision format differences change both accuracy and throughput characteristics.

- Google (TPU v7+) and Meta (MTIA) each present their own in-house silicon trajectories, showing that hyperscalers see long-term value in bespoke processors for both cost and performance at scale.

Strengths and likely practical advantages

- Inference-first optimization — Maia 200’s choice to tune for FP4/FP8 and token-level throughput is a practical match to how many production LLMs are used, particularly for high-volume serving. This specialization can produce substantial cost savings where models have predictable inference patterns.

- Memory-centric architecture — the combination of high HBM3e capacity/bandwidth and sizeable on-chip SRAM is a proven way to reduce stalls and increase utilization on real models. This is a direct response to the biggest performance limiter in production inference: data movement.

- Integrated software and Triton support — offering a PyTorch path and a Triton compiler lowers friction for developers, which is crucial for adoption inside Microsoft and for any tier of customers who will be allowed access.

- Performance-per-dollar focus — Microsoft claims a 30% improvement in performance-per-dollar relative to its current fleet, a metric that matters more for cloud customers and internal economics than peak FLOPS alone. This reflects the company’s focus on token economics for large language models. Vendor claims are corroborated by multiple news outlets repeating Microsoft’s numbers, but independent benchmark validation remains necessary.

Risks, caveats, and unknowns

- Vendor-declared performance vs. independent benchmarks — Microsoft’s FP4/FP8 numbers and “3× Trainium Gen 3 FP4” claims come from vendor slides and press releases. Independent, reproducible benchmarks (MLPerf or third-party workloads) are necessary to validate real-world claims across latency-sensitive and throughput scenarios. Until public benchmarks appear, treat vendor-supplied metrics as directional rather than definitive.

- Precision tradeoffs — running inference at FP4 can dramatically increase throughput, but not every model or workload tolerates aggressive quantization without retraining, calibration, or other compensations. Microsoft’s claims of FP4 accuracy parity on typical LLMs are plausible, but model authors should plan validation work per-model. Blindly moving to lower precision without evaluation risks subtle accuracy regressions, hallucination differences, or changes in downstream behavior.

- Ecosystem inertia — NVIDIA’s CUDA ecosystem is decades in the making. While Triton and ONNX lower migration costs, many third‑party kernels, optimizers, and specialized libraries remain CUDA-first. Enterprises that require a broad third‑party ecosystem for advanced workloads may still need NVIDIA-based options for some time.

- Access and vendor lock-in — Microsoft’s historical approach with custom silicon has been to prioritize internal services and Azure customers. The long-term availability of Maia-based instances to third parties is a commercial decision; customers should be cautious about any assumption that a chip available inside Azure will be purchasable as hardware or broadly portable across clouds. This is a common pattern among hyperscalers and an operational risk for multi-cloud strategies.

- Supply chain and cost risks — cutting-edge process nodes (3nm) are expensive to source and come with yield and supply constraints. While in-house design reduces dependence on external vendors for architecture, it still ties Microsoft to TSMC’s capacity and the macroeconomic cycle of leading-node wafers. That said, Microsoft clearly judged the long-term economics favorable enough to invest.

What this means for Azure customers and enterprise AI operations

If Microsoft follows through on Maia 200’s promise and integrates it widely across Azure, customers should expect:- Lower token costs for high-volume, predictable inference workloads — Microsoft’s 30% perf-per-dollar claim targets exactly this outcome.

- Faster response times for services backed by Maia (Copilot, Foundry) due to lower-latency, higher-utilization inference stacks.

- A more heterogeneous cloud offering, where Azure operators choose Maia for massive serving pools and NVIDIA for mixed, GPU-optimized workloads requiring CUDA.

- Model validation pipelines to test low-precision inference fidelity,

- Performance engineering cycles to tune kernels with Triton or NPL where necessary, and

- A multi-accelerator deployment strategy if latency, ecosystem dependencies, or third-party tools require GPUs for specific workloads.

Strategic implications across the industry

- Hyperscalers will keep building custom silicon — Maia 200 reinforces that custom AI accelerators are now strategic infrastructure assets for cloud providers, not one-off experiments. Expect continued multi-generation investment and tighter co-design between models and hardware.

- The software layer becomes the battleground — chips alone don’t win customers; integrated toolchains and migration paths do. Microsoft’s Triton + PyTorch + NPL strategy is an effort to lower switching costs and capture developer mindshare. Success here will hinge on how well Microsoft replicates the rich tooling third parties expect around CUDA.

- Price competition and specialized fabrics — the move toward commodity-like interconnects (standard Ethernet with a custom transport layer) signals a pragmatic approach: reduce the cost of scale while retaining tight coupling for collective operations. Other vendors will watch whether this approach yields the promised latency, reliability, and TCO advantages.

Practical checklist for engineering leaders

- Evaluate model tolerance for low-precision (FP8/FP4) quantization with holdout datasets before committing to Maia-optimized deployments.

- Allocate engineering time to kernel validation — Triton may allow porting without massive rewrites, but production-level latency/p50/p99 guarantees still require tuning.

- Consider a phased migration: run Maia-accelerated instances for high-volume serving paths first, keep GPUs for complex, experimental, or third-party-dependent workloads.

- Watch for independent MLPerf-style benchmarks and third-party reports before making major procurement decisions based solely on vendor FLOPS claims.

Conclusion

Maia 200 is a concrete expression of a broad industry trend: hyperscalers are turning AI silicon into a primary lever of cost, capability, and differentiation. Microsoft’s chip stacks contemporary semiconductor advances (TSMC 3nm) with systems-level engineering — high HBM3e capacity, on-die SRAM, a tile-based compute fabric, and a Triton-friendly SDK — to deliver a tightly integrated inference platform. If the vendor-reported numbers hold up in independent, real-world benchmarks, Maia 200 will materially shift the economics of large-scale token generation on Azure.That said, the usual caveats apply: vendor claims need independent validation; FP4/FP8 migration requires careful per-model testing; and CUDA’s software ecosystem remains a formidable moat. For enterprises, the prudent path is one of measured experimentation: pilot Maia-accelerated serving for workloads that are already robust to quantization and that would benefit most from reduced token costs, while retaining GPU options for workloads that demand the NVIDIA ecosystem or higher precision.

Maia 200 isn’t just another silicon announcement — it’s the next chapter in cloud providers’ long march to owning not only the data center but the math that runs on it. Whether that translates into better price-performance for customers will depend on Microsoft’s rollout, the availability of Maia-optimized instances, and the outcomes of independent validation. For now, Maia 200 raises the stakes in the custom-silicon race and makes the case that in the era of generative AI, the company that co-designs models, software, and chips can command meaningful advantages.

Source: YourStory.com Microsoft Maia 200 and the ongoing evolution of custom AI silicon