Astera Labs’ Leo CXL Smart Memory Controllers are now powering customer evaluation of CXL-attached memory in Microsoft Azure’s M‑series virtual machines preview, a move that promises to reshape how cloud operators address the “memory wall” for memory‑hungry workloads while also exposing a raft of practical and strategic challenges that will determine whether CXL becomes a mainstream cloud fabric or a niche performance play.

Background / Overview

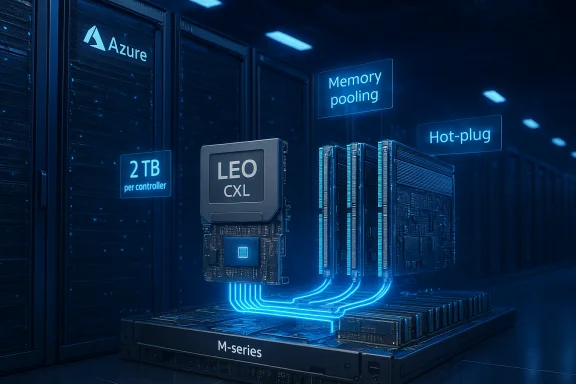

Compute Express Link (CXL) is an industry open standard designed to extend coherency and memory semantics over PCIe physical links, enabling hosts to attach, share, and pool memory that is not directly soldered to the CPU. With the arrival of CXL 2.0, the specification added critical capabilities — switching, memory pooling, device partitioning, and EDSFF form‑factor support — that turn point‑to‑point memory expansion into an architecture that can be shared at rack and fabric scale. These features are intended to let cloud providers expand memory capacity beyond the physical limits of CPU DIMM slots, enabling larger in‑memory datasets to run with lower total cost of ownership.Astera Labs’ announcement on November 18, 2025, confirms that its Leo CXL Smart Memory Controllers are the hardware foundation enabling customers to evaluate CXL memory expansion with Azure M‑series VMs in a preview environment. The company states Leo supports CXL 2.0 and can present up to 2 TB of CXL‑attached memory per controller, using DDR5‑5600 RDIMMs on PCIe add‑in or purpose‑built hardware. Astera Labs and Microsoft position the Azure M‑series preview as the industry’s first announced deployment of CXL‑attached memory, and the stated use cases include in‑memory databases, big data analytics, AI inference, and KV cache for large language models (LLMs).

This is not a small step: if deployed at scale, CXL memory expansion changes the system‑level economics of AI and database workloads. But the road from preview to production is long, and multiple technical, operational, and market factors will determine how broadly and quickly the industry adopts CXL in public cloud settings.

Why CXL matters: the memory wall and cloud economics

The “memory wall” refers to the growing gap between compute and memory capacity: CPUs and accelerators grow in computational power, but platform memory is constrained by DIMM slot count, thermal limits, and cost. For many modern data workloads — large‑scale in‑memory databases, recommendation systems, and AI inference at scale — hitting that limit forces either expensive multi‑CPU configurations or slow, storage‑backed tiers that degrade latency and throughput.CXL aims to relax that constraint by letting servers attach additional DRAM‑class devices outside the CPU package while maintaining memory semantics that make the extra capacity useful without a complete software rewrite. Key benefits enabled by CXL 2.0 include:

- Memory expansion beyond CPU DIMM capacity, allowing larger datasets to be kept in low‑latency memory.

- Memory pooling and device partitioning, allowing multiple hosts to share or carve up memory capacity dynamically.

- Hot‑plug and switching support that facilitates operational flexibility at hyperscale.

- Support for new form factors (e.g., EDSFF) and add‑in card deployment models that use existing PCIe slots.

The announcement: what Astera Labs and Azure are offering in the preview

Astera Labs says its Leo controllers are available in the Azure M‑series preview to enable customer evaluation of CXL memory expansion. The concrete technical claims in that announcement are:- Support for CXL 1.1 and CXL 2.0 protocols.

- Up to 2 TB of CXL‑attached memory capacity per controller (via 4× DDR5‑5600 RDIMM on certain Leo A‑Series or 2‑channel configurations on other form factors).

- CXL link widths and speeds consistent with PCIe‑based CXL links used in modern servers, enabling high throughput and low latency relative to conventional storage tiers.

- Tools for management and observability (Astera’s COSMOS suite) intended to support fleet‑scale diagnostics, telemetry, and RAS (reliability, availability, serviceability).

Verification note (industry cross‑check): The Leo product pages and company technical briefs list DDR5‑5600 support, form factor details, and 2 TB capacity per device. Independently, vendor and consortium documentation about CXL 2.0 confirms the memory pooling and switching capabilities that make such deployments possible.

Who benefits and which workloads matter most

Astera Labs and Microsoft call out a similar set of target workloads. The most immediate beneficiaries are:- In‑memory databases (OLTP and OLAP) that need more main‑memory than a CPU socket can provide.

- AI inference (especially LLMs) where KV cache and large embedding tables are memory bound rather than compute bound.

- Big data analytics and streaming frameworks that have large working sets.

- Machine learning training and feature stores where transient memory demands spike.

The technical trade‑offs: latency, coherency, and performance determinism

CXL gives you capacity and flexibility — but it does so with trade‑offs that operators will need to measure and understand.- Latency profile: CXL‑attached DRAM remains slower than CPU‑attached DIMMs. The difference is implementation dependent, but expectation management is critical: CXL aims for DRAM‑like latency, not identical latency, and measured latency will vary by controller, link topology, switch depth, and software stack.

- Bandwidth and contention: Shared pooling and multi‑host access invite contention dynamics. For high‑bandwidth, low‑latency flows (e.g., GPU‑GPU fabrics), design choices such as interleaving, QoS, and switch buffering will matter.

- Cache coherency and semantics: CXL offers caching and memory semantics (CXL.cache, CXL.mem) to maintain coherent access between hosts and devices, but ensuring correctness in complex host/device combinations — especially across virtualization and multi‑tenant boundaries — requires careful platform engineering.

- NUMA and OS integration: Adding large secondary memory pools changes system NUMA characteristics and can confuse kernel memory allocators, scheduler heuristics, and garbage collectors. Effective use will require operating system and hypervisor updates — plus application tuning.

- Interoperability and ecosystem maturity: CXL is an ecosystem play. Memory modules, retimers, switches, memory controllers, host processors, and platform firmware all need to interoperate. Early preview deployments will be valuable for uncovering edge cases.

Operational realities in the Azure preview

A preview environment is the right place to exercise those operational mechanics. Customers testing Azure M‑series with Leo controllers should plan to evaluate:- Latency curves under realistic workload mixes (local DRAM vs CXL memory transition paths).

- Bandwidth and contention characteristics for pooled memory under concurrent access.

- Failure and recovery modes for both controllers and remote memory — how the platform surfaces errors and how quickly recovery happens.

- Observability and telemetry data from COSMOS or provider tools to monitor bit error rates, link health, and thermal behavior.

- Integration with virtualization and container stacks: how memory hot‑add, reclamation, and partitioning behave in VMs and containers.

Astera Labs’ product specifics and roadmap context

Astera’s Leo family is positioned as a purpose‑built memory controller line for cloud and AI platforms. Product materials highlight:- Multiple Leo form factors, including PCIe add‑in cards and system validation boards.

- Support for DDR5‑5600 RDIMMs, providing up to 2 TB capacity on certain configurations.

- COSMOS management stack for telemetry, diagnostics, and fleet management.

- Interoperability testing with major DRAM and XPU vendors.

Market reaction, financial context, and analyst views

Astera Labs reported a strong Q3 2025 performance (reported on November 4, 2025) with record revenue and earnings that materially exceeded consensus. The headline metrics that investors focus on are:- Q3 2025 revenue in the region of $230.6 million, roughly double year‑over‑year.

- Adjusted earnings per share near $0.49 (depending on GAAP vs non‑GAAP presentation).

- Solid gross and operating margins reported for the period.

The Azure M‑series preview announcement dovetails with positive financial momentum, offering a concrete hyperscaler engagement that validates differentiation in CXL and fabric technologies. Yet investors and operators will evaluate whether preview engagements translate into recurring hyperscaler design wins and high‑volume production shipments.

Competition, ecosystem players, and who’s working on CXL

CXL adoption is an ecosystem effort. Memory module suppliers, retimer and switch vendors, CPU and accelerator vendors, and hyperscalers all play roles. Key dynamics to watch:- Multiple silicon vendors are developing CXL‑capable controllers and switches; interoperability testing across vendors will be decisive.

- Memory module and add‑in card suppliers are adapting designs (EDSFF, AIC) to support high‑capacity CXL modules.

- System integrators and hyperscalers are conducting in‑house validation and custom platform integration — early preview programs with cloud vendors can set implementation patterns.

- Platform software (Linux kernel, hypervisors, cloud orchestration) must evolve to support hot‑plug, pooling APIs, and memory management semantics.

Risks and caveats: what could slow or complicate adoption

Adopting CXL at cloud scale faces several concrete hurdles:- Performance determinism: For latency‑sensitive services, any additional tail latency introduced by remote memory could cause SLA issues. Only measured testing will clarify the practical impact.

- Software and orchestration: Kernel, hypervisor, and container runtimes must understand CXL resources and be able to allocate and reclaim memory safely across multi‑tenant environments.

- Security and multi‑tenant isolation: When memory is pooled across hosts, secure partitioning and erase‑on‑reclaim semantics become essential for tenant isolation.

- Interoperability and standard maturity: Although CXL 2.0 provides features like pooling and switching, diverse vendor implementations may introduce edge cases that take time to resolve.

- Operational complexity: Fleet management, firmware updates, failure isolation, and lifecycle operations for CXL devices add new operational domains for cloud operators.

- Competitive technology paths: Alternative approaches such as denser CPU sockets, faster local DRAM, or proprietary fabrics could compete for the same workloads and slow CXL adoption if they deliver better integration or economics.

- Cost and supply dynamics: High‑capacity RDIMMs, controllers, and switches add BOM cost and power consumption; net TCO benefits depend on real‑world consolidation and utilization improvements.

Where this fits in a broader industry timeline

CXL as a standard has evolved rapidly: initial point‑to‑point implementations (CXL 1.x) were followed by the CXL 2.0 spec that introduced pooling and switching. Many vendors are still moving from demonstration to production silicon and system integration. The preview deployment in Azure M‑series represents an important milestone, but it remains a cautious one: preview implies evaluation, not full production readiness.Key milestones to watch over the coming quarters:

- Public benchmarking results from Azure’s M‑series preview that quantify latency, throughput, and TCO impacts.

- Additional hyperscaler announcements or GA services that adopt CXL‑attached memory.

- Shipments and ramp narratives for products like Astera’s Scorpio X and Leo controllers — particularly Q4 2025 and 2026 ramp expectations tied to chip and platform availability.

- Ecosystem software updates in Linux kernels, hypervisors, and major cloud orchestration systems to support pooled memory semantics.

- Third‑party interoperability test results and cross‑vendor validation efforts.

Practical guidance for practitioners and decision makers

For cloud architects, system integrators, and enterprise IT teams evaluating CXL options, a pragmatic approach during preview phases is critical:- Prioritize realistic workload testing: run production‑like in‑memory databases and inference pipelines, not microbenchmarks that hide tail behaviors.

- Measure tail latency and variance as primary decision metrics — average latency masks the worst‑case behaviors that break SLAs.

- Test operational failure modes: controller resets, link drops, and pool reclamation to understand maintenance windows and recovery automation needs.

- Demand observability: rich telemetry at link, device, and workload levels is essential for debugging and capacity planning.

- Model TCO across multiple scenarios: buyer’s remorse can be costly if the new hardware doesn’t produce the expected consolidation.

- Plan for phased rollouts: use CXL where the benefits are clear (e.g., KV caches for LLMs) while avoiding wholesale platform redesign until the ecosystem matures.

Strategic implications for Astera Labs and cloud vendors

For Astera Labs, the Azure preview is both a technical validation and a commercial signal. If previews evolve into GA services and design wins, the company’s differentiated system silicon and management software (COSMOS) could capture substantial rack‑scale connectivity dollar content. Analysts have already tied future revenue expectations to Scorpio X and PCIe Gen‑6 ramps.For Microsoft and other cloud vendors, offering CXL‑attached memory opens a new dimension of product differentiation: on‑demand large memory instances without requiring more CPUs. That can be a competitive advantage for database and AI customers. However, cloud vendors must be careful to document performance expectations, pricing models, and operational norms — otherwise, customer experience risk is material.

Conclusion

The collaboration between Astera Labs and Microsoft to enable Leo CXL Smart Memory Controllers in an Azure M‑series VMs preview is an important step toward practical, large‑scale CXL deployments in cloud environments. The technical blueprint is now in place: CXL 2.0 supports the pooling and switching primitives needed to move memory beyond the socket, and the Leo controllers provide a concrete implementation that supports DDR5‑5600 and up to 2 TB per controller.Yet preview status matters: the announcement is a validation of the technology stack and an invitation to customers to evaluate, not a declaration of mass production. The gains — bigger in‑memory datasets, improved utilization, and better TCO for certain workload classes — are real and measurable. At the same time, ecosystem maturity, software integration, latency determinism, and operational complexity remain open questions that will be answered only by broad testing and measured production rollouts.

In short, CXL memory expansion is promising and potentially transformational for memory‑bound cloud workloads, but the critical work now shifts to rigorous benchmarking, cross‑vendor interoperability testing, and careful, phased operational adoption. The Azure preview will be one of the first public windows into how those factors play out in real customer workloads.

Source: Investing.com UK Astera Labs’ memory controllers power Microsoft Azure CXL preview By Investing.com